Atualmente, o desenvolvimento de sistemas de inteligência artificial (IA) enfrenta desafios em termos de escala, exigindo quantidades massivas de memória para garantir que os chips de processamento possam compartilhar dados rapidamente. As GPUs tradicionais, não projetadas originalmente para modelos de IA, requerem múltiplas GPUs conectadas por meio de redes de alta velocidade para suportar grandes modelos de linguagem (LLMs), resultando em baixas velocidades de transferência de dados e alto consumo de energia.

Para superar o gargalo das GPUs, empresas como a Cerebras, na Califórnia, desenvolveram processadores em nível de wafer. Esses chips são grandes, contendo enormes quantidades de memória on-chip e centenas de milhares de núcleos. No entanto, os chips em nível de wafer por si só são insuficientes; sistemas de software especializados também são necessários. O WaferLLM, desenvolvido em colaboração entre a Universidade de Edimburgo e a Microsoft Research, visa executar LLMs em larga escala de forma eficiente em chips em nível de wafer.

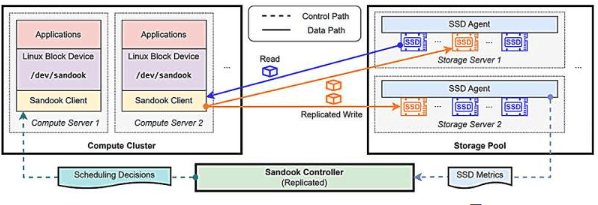

O WaferLLM emprega três novos algoritmos para decompor grandes operações matemáticas em partes menores, permitindo que núcleos adjacentes as processem em conjunto e transmitam informações localmente, evitando a redução de velocidade causada pela comunicação de longa distância. Simultaneamente, introduz uma nova estratégia para distribuir diferentes partes do LLM (Modelo de Nível de Linha) por centenas de milhares de núcleos, coordenando o processamento e a comunicação para garantir a operação eficiente do chip. Esses ajustes, testados no Centro Internacional de Dados de Edimburgo, resultaram em velocidades de geração de texto aproximadamente 100 vezes mais rápidas para chips em nível de wafer, latência dez vezes menor e o dobro da eficiência energética em comparação com um cluster de 16 GPUs.

Embora as GPUs possuam um ecossistema de software maduro, os chips em nível de wafer são mais adequados para cargas de trabalho que dependem de latência ultrabaixa, modelos ultragrandes ou alta eficiência energética. Enquanto isso, a tecnologia de GPU continua a avançar. Uma implicação mais ampla é que a infraestrutura de IA está se tornando um problema de codesign, exigindo que hardware e software evoluam em conjunto. Repensar a pilha de software é crucial para desbloquear a próxima geração de desempenho de IA. Para o público, os sistemas de IA suportarão mais aplicações que antes eram lentas ou caras, e a transição para a computação em nível de wafer marca uma nova fase no desenvolvimento de IA.