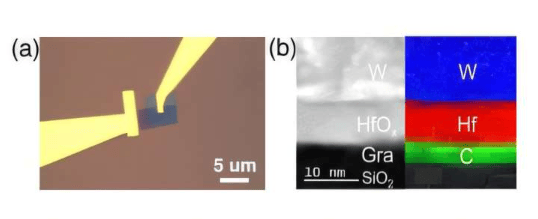

Uma equipe de pesquisadores da Universidade Stanford, da Universidade Carnegie Mellon, da Universidade da Pensilvânia e do MIT, em colaboração com a fundição de wafers SkyWater Technology, fabricou com sucesso um novo chip integrado monolítico 3D. Essa conquista demonstra uma melhoria significativa de desempenho em relação aos chips 2D tradicionais.

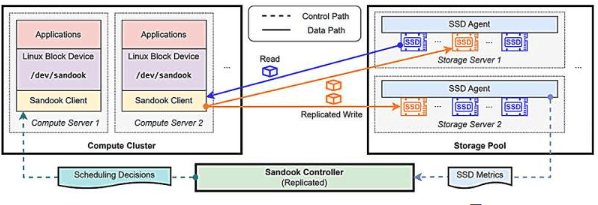

Ao contrário dos designs planos convencionais atuais, os componentes principais deste chip protótipo são empilhados verticalmente, como andares de um arranha-céu, permitindo a transmissão de dados em alta velocidade por meio de interconexões verticais de alta densidade. O chip integrado monolítico 3D apresentou desempenho aproximadamente quatro vezes superior ao de chips 2D comparáveis em testes de hardware. A pesquisa foi apresentada na 71ª Conferência Internacional de Dispositivos Eletrônicos do IEEE (IEDM 2025), em São Francisco.

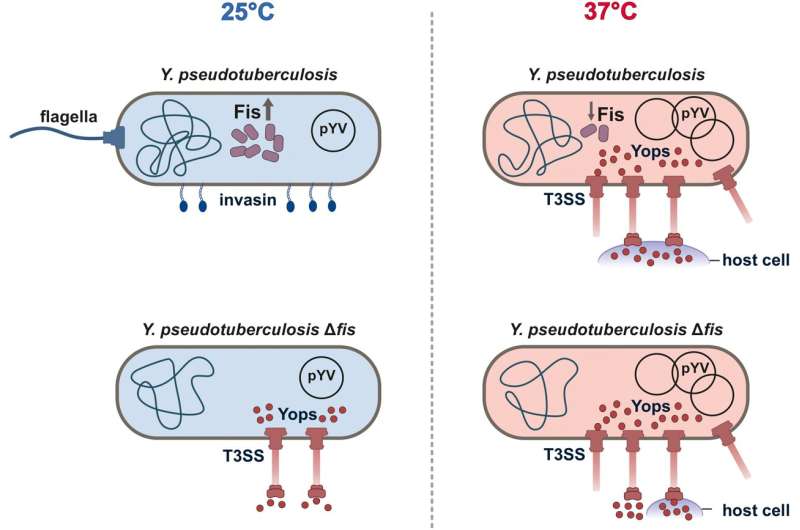

As arquiteturas de chips tradicionais enfrentam desafios como o "barreira da memória" e os "gargalos de miniaturização". "Ao integrar verticalmente memória e computação, podemos transferir mais informações muito mais rapidamente, assim como um elevador em um prédio alto permite que vários moradores se desloquem entre os andares simultaneamente", explicou Tatagata Srimani, autor sênior do artigo e professor assistente da Universidade Carnegie Mellon.

A chave para esse avanço reside na fabricação monolítica, que envolve o empilhamento direto e contínuo de múltiplas camadas de circuitos em um único wafer dentro de uma fundição comercial, em vez de colar vários chips separados posteriormente. "Isso inaugura uma nova era na fabricação e inovação de chips", disse Subashish Mitra, professor da Universidade Stanford e principal autor do artigo. "São avanços como este que nos permitem alcançar o aumento de desempenho de hardware de 1.000 vezes necessário para os futuros sistemas de IA." Mark Nielsen, vice-presidente de desenvolvimento tecnológico e operações da SkyWater, acredita que isso demonstra a viabilidade da produção nacional em larga escala de arquiteturas integradas 3D avançadas.

Pesquisadores simularam projetos com um número ainda maior de camadas, demonstrando melhorias de desempenho de até 12 vezes ao lidar com tarefas do mundo real derivadas de grandes modelos de linguagem. Essa arquitetura monolítica de chip integrado 3D abre um caminho viável para alcançar melhorias de centenas ou até milhares de vezes nas métricas combinadas de velocidade de computação e eficiência energética (produto energia-atraso).