A Faculdade de Engenharia da Universidade Nacional de Seul anunciou que uma equipe de pesquisa liderada pelo Professor Lee Cheol-ho, do Departamento de Engenharia Elétrica e de Computação, desenvolveu um roteiro abrangente para "empilhamento de portas". Como tecnologia central para transistores bidimensionais (2D), o "empilhamento de portas" está se tornando um foco de atenção para dispositivos semicondutores de próxima geração. A pesquisa foi publicada na Nature Electronics.

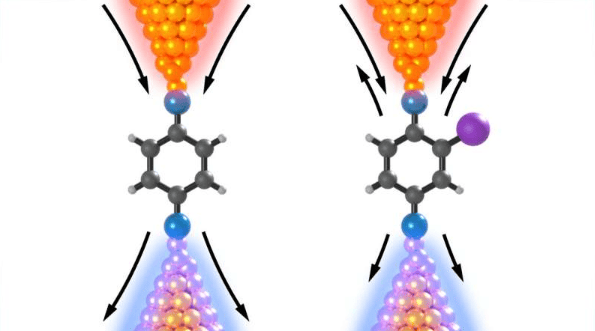

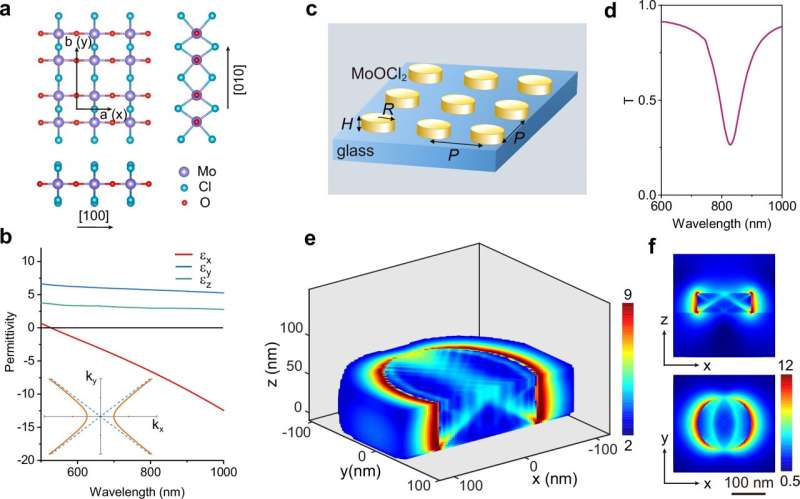

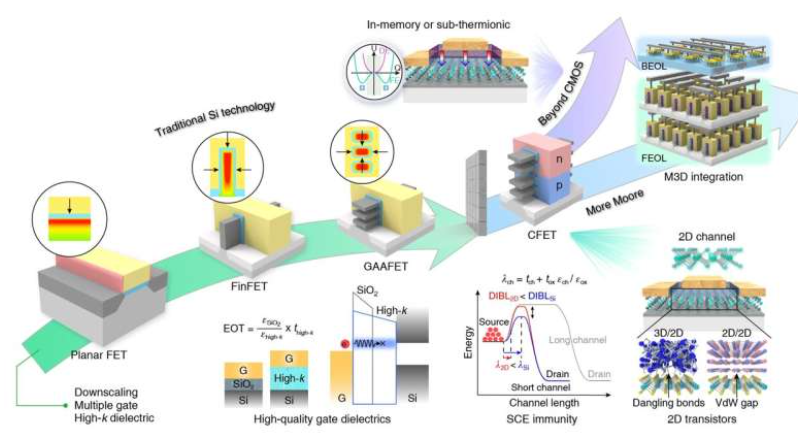

Atualmente, a maioria dos semicondutores depende da tecnologia CMOS baseada em silício, mas à medida que a tecnologia avança para o reino subnanométrico, as limitações físicas e eletrostáticas estão se tornando cada vez mais proeminentes. Semicondutores 2D, que mantêm propriedades elétricas em espessuras atômicas, são considerados materiais de canal que superam o silício. Eles atraíram a atenção de empresas líderes globais de semicondutores, incluindo Samsung e TSMC, e foram incluídos no roteiro da tecnologia pós-silício. No entanto, o maior desafio enfrentado pela comercialização de semicondutores 2D é a tecnologia de integração de empilhamento de portas, cuja qualidade impacta diretamente o desempenho e a estabilidade do dispositivo.

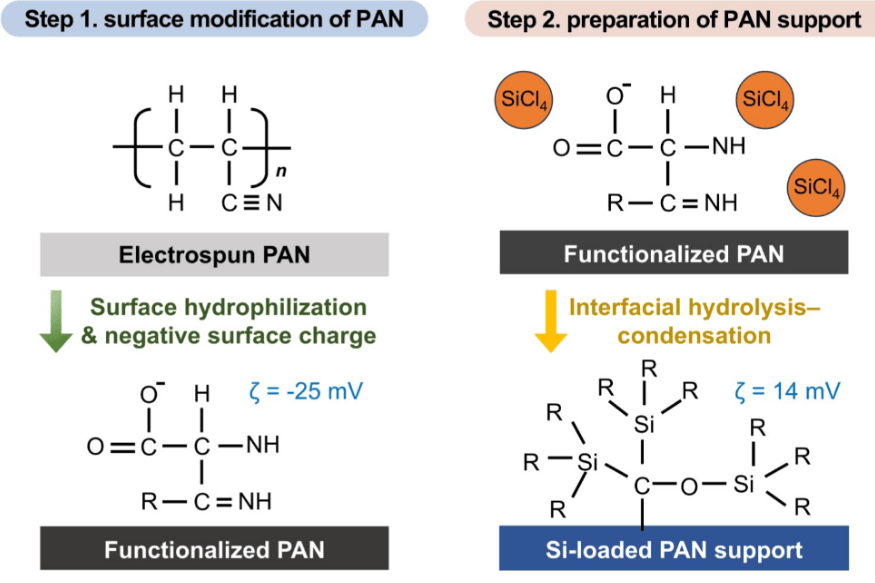

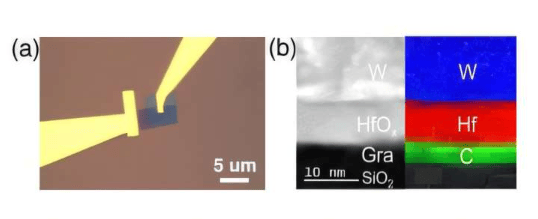

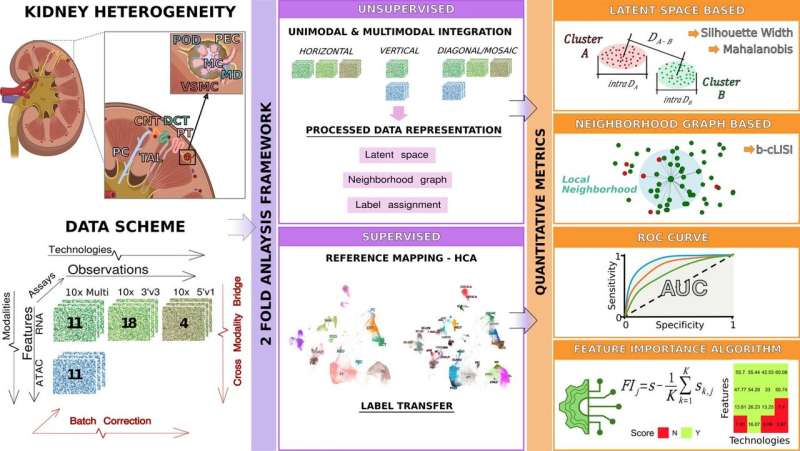

A equipe do Professor Lee analisou diversos métodos de integração de pilhas de portas e conduziu benchmarking quantitativo com base em métricas de desempenho, como densidade de armadilhas de interface e espessura de óxido equivalente. O estudo categorizou os métodos de integração de pilhas de portas em cinco categorias e os comparou com as metas do Roteiro Internacional para Dispositivos e Sistemas (IRDS) para formar um roteiro de desenvolvimento sistemático. A pesquisa também demonstra o potencial da tecnologia de empilhamento de portas ferroelétricas para dispositivos de próxima geração e destaca a viabilidade de aplicações industriais práticas, incluindo requisitos como compatibilidade de back-end-of-the-line (BEOL) e deposição em baixa temperatura.

Esta pesquisa não apenas fornece um modelo para o desenvolvimento de semicondutores de próxima geração, mas também demonstra a viabilidade de transistores de ultrabaixo consumo de energia e alto desempenho e propõe diretrizes técnicas específicas para integração 3D monolítica e processos compatíveis com BEOL. O Professor Li declarou: "Alcançar um empilhamento de portas de alta qualidade é fundamental para a comercialização de transistores 2D. Esta pesquisa fornece um modelo padrão para superar esses desafios, o que tem implicações significativas tanto para a academia quanto para a indústria."